Chip Gallery

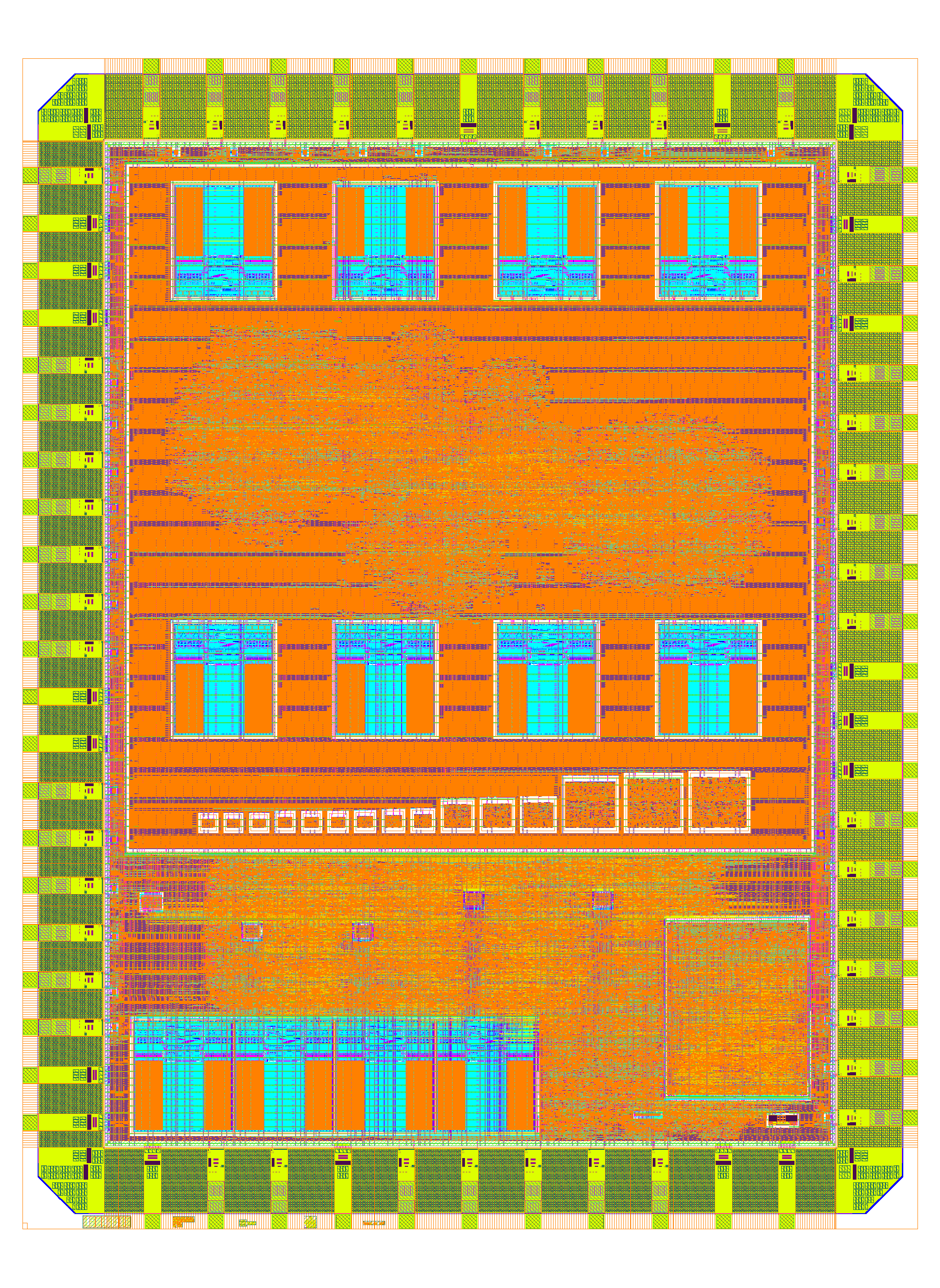

Greyhound

A RISC-V SoC with tightly coupled eFPGA on IHP SG13G2

Greyhound has been submitted to the IHP-Open-DesignLib for fabrication.

- Designed using the IHP Open Source PDK

- SoC:

- CV32E40X RISC-V core from the OpenHW group

- 8kB SRAM

- QSPI Flash Controller for XIP (w. cache)

- QSPI PSRAM controller

- Highly Configurable UART

- Fabric Config Peripheral

- Fabric Peripheral

- FABulous eFPGA

- 32x I/Os

- 784x LUT4 + FF (w. carry chain)

- 98x MUX (Either 1xMUX8, 2xMUX4 or 4xMUX2)

- 7x SRAM (32 bit-wide, 4kB deep)

- 7x MAC (8bit*8bit + 20bit)

- 14x Register file (32x4bit each, 1w1r1r)

- 1x Global clock network

- 1x WARMBOOT

- 1x CPU_IRQ

- 4x CPU_IF

Second Minimal Fab Design Contest

Counter, Ringo, ROM and Stdcells

I submitted three different designs to the second Minimal Fab Design Contest.

- Designed using the open source ICPS PDK

- Created a minimal stdcell library

- Wrote a simple Place and Route tool

- Created two submissions with a counter, ring-oscillator and ROM using my stdcell library and PnR tool

- Created one submission for the characterization of some of the stdcells

One Sprite Pony (IHP)

SVGA sprite generator

An updated version of One Sprite Pony has been submitted to Tiny Tapeout IHP 0.2

- SVGA 800x600 60Hz output with 2 bits per color (internally reduced to 100x75)

- Sprite with 12x12 pixels

- 4 different colors (6 bit rrggbb)

- 4 different backgrounds

- Uses clock gating for the sprite shift register

- Simplified SPI interface

- Assign new sprite positions only on new line

- Clamp x and y position to prevent uncontrolled shifting of the sprite data

AICD Playground

A simple mixed-signal design

AICD Playground has been submitted to Tiny Tapeout 08

- 8-bit CPU with 64 bytes of work memory

- Levelshifters in both directions

- 3.3V R2R-DAC

- 3.3V Comparator

- Can be programmed as SAR-ADC

Wirecube

VGA wirecube

Wirecube has been submitted to Tiny Tapeout 08 for the demoscene competition.

- VGA output at 640x480 @ 60 Hz

- Draws lines while racing the beam

- Displays a rotating cube in wireframe rendering

TGFF

Transmission-Gate D Flip-Flop

TGFF has been submitted to the first Minimal Fab Design Contest. It was manufactured, worked as designed and won the special award.

- Designed using the open source ICPS PDK

- Uses the provided element array chip

- Only metal 1 was used to connect the devices

Tiny Shader

VGA shader unit

Tiny Shader has been submitted to Tiny Tapeout 06

- VGA output at 640x480 @ 60 Hz

- 64x48 internal resolution

- 10 instructions for each pixel

- No framebuffer used

- Animations possible

- SPI Receiver

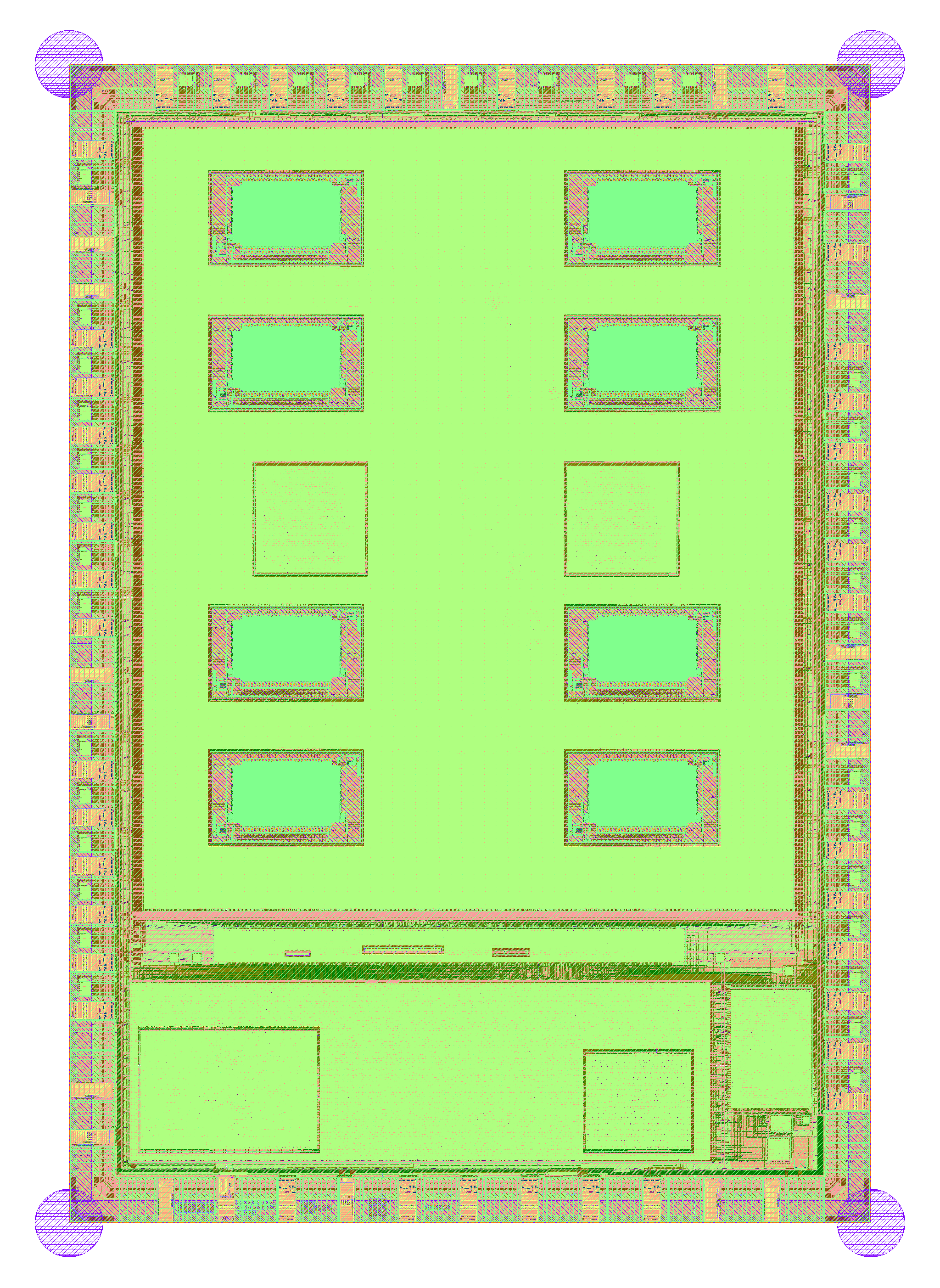

LeoSoC GFMPW-1

An SoC with TRNGs

LeoSoC has been submitted to GFMPW-1

The SoC contains the following:

- Two RV32I cores running in parallel

- 32 word direct-mapped instruction cache for each core

- 4kB of shared memory

- SPI flash controller

- 2 UARTs

- 1 GPIO controller (24 I/Os)

- 15 different TRNGs

One Sprite Pony

SVGA sprite generator

One Sprite Pony has been submitted to Tiny Tapeout 05

- SVGA 800x600 60Hz output with 2 bits per color (internally reduced to 100x75)

- 40 MHz or 10 MHz operation depending on configuration

- Sprite with 12x12 pixels

- 4 different colors (6 bit rrggbb)

- 4 different backgrounds

- SPI Receiver

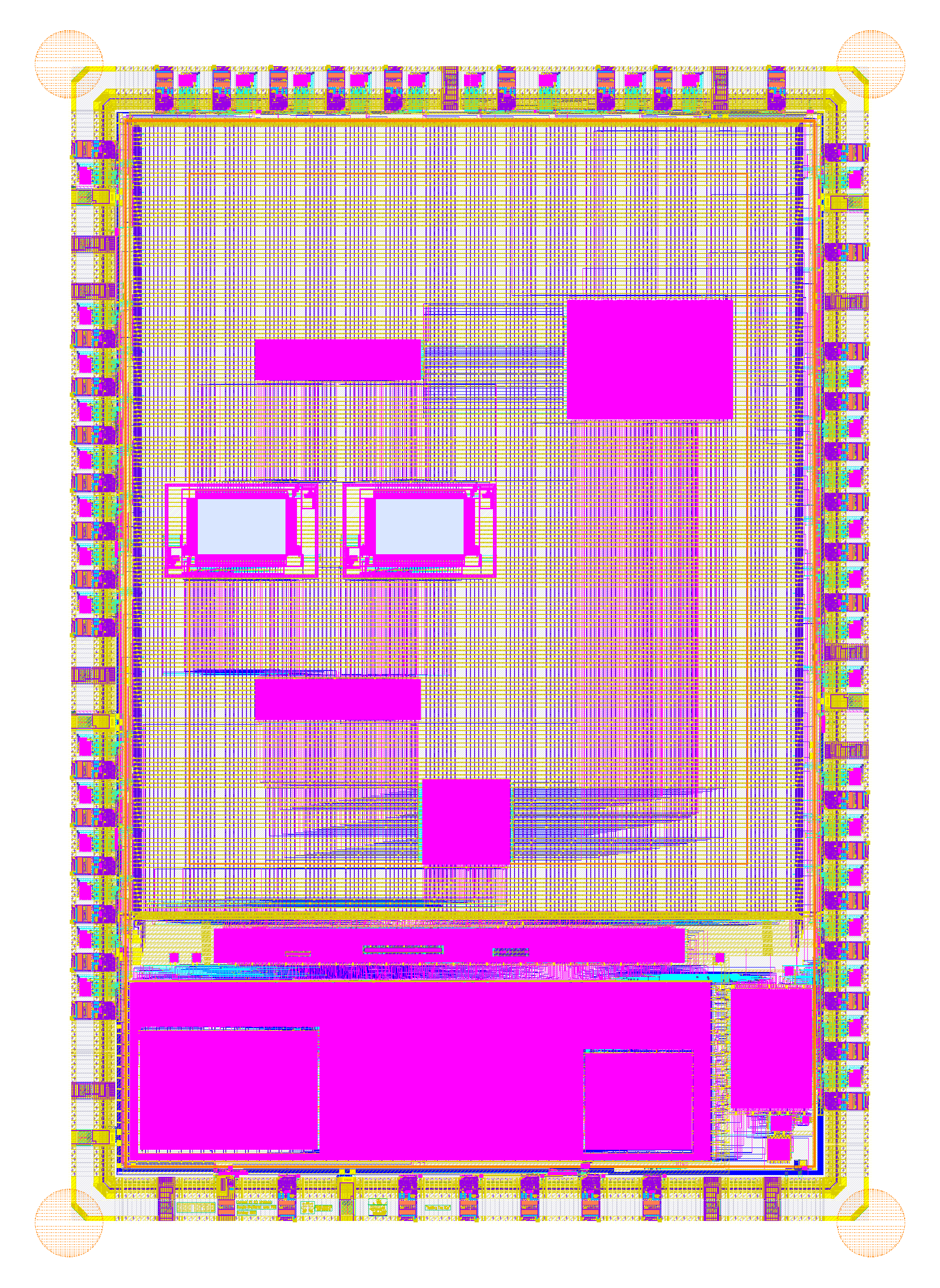

LeoSoC

A simple SoC

LeoSoC has been submitted to Efabless Open MPW-8

The SoC contains the following:

- 1 LeoRV32 Core (RV32I)

- 8 kB Work RAM

- 8 kB Video RAM (can also be used as Work RAM)

- SVGA Core (800 x 600, 40 MHz)

- UART (9600 baud)

- Blink (blink an LED)

Waveform Generator

My first chip

Waveform Generator has been submitted to Efabless Open MPW-7

A generic waveform generator divided into stimulus and driver units that can be arbitrarily interconnected.

Currently the following blocks are implemented:

Stimuli

- wfg_stim_sine

- wfg_stim_mem

Driver

- wfg_drive_spi

- wfg_drive_pat

Various

- wfg_interconnect

- wfg_core

- wfg_subcore